在过去的几十年中,由于信号采集系统的不断增加和永不满足的带宽需求,尽管速度很慢,但高速模数转换器(ADC)性能指标发生了很大变化,尽管速度缓慢。ADC性能测量的方式也发生了变化。

在20世纪80年代,我们主要根据其直流规格(如差分和积分非线性(DNL和INL))来判断ADC。在20世纪90年代,我们主要根据其信噪比(SNR)来判断ADC。虽然无杂散动态范围(SFDR)也是一个重要的ADC参数,但噪声谱密度(NSD)是当今高速和每秒千兆(GSPS)ADC可用于定义其性能的又一全面规范。

虽然NSD已经用很长时间来定义转换器的噪声,但作为新型高速ADC的标题规范,许多系统设计人员可能都会觉得新颖。对于选择高速ADC时专注于其他规范的工程师来说,NSD也可能是一个完全陌生的概念。下面是一些工程师的典型问题的答案,这些答案有助于说明为什么他们应该更多地了解这种ADC性能指标:

在奈奎斯特速率ADC数据手册中,我已经看到了NSD规范,但我从未真正理解它的意义及其重要性。什么是噪声频谱密度?

许多年来,NSD一直被用作许多ADC数据手册首页的性能参数。您可能已经注意到,它是一个相对较大的负数,以dBFS / Hz或dBm / Hz定义。在ADC的NSD数据表中可以观察到的典型范围可以在-140 dBFS / Hz到-165 dBFS / Hz之间。然而,这最终将由ADC的SNR性能和采样率来定义,这将在本文稍后部分进行描述。

来自ADC的SNR被定义为在ADC的输入端看到的信号功率与总非非信号功率的对数比。相对于ADC满量程输入,信噪比被描述为SNRFS。非信号功率有几个组件,如量化噪声,热噪声和ADC设计本身内的小误差。由于ADC使用非线性过程将连续信号转换为离散电平,量化噪声本身就会产生。量化噪声是通常用正弦波表示的实际模拟输入与最小离散步或最低有效位(LSB)的值之差。

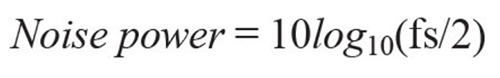

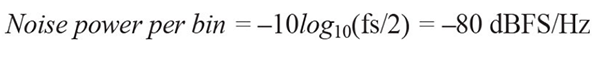

NSD定义了在ADC输入端采样的整个噪声功率,单位带宽。对于奈奎斯特速率ADC,这种噪声分布在整个奈奎斯特频带上,这个频带等于fs的一半,采样频率或fs / 2。

NSD的单位表示什么?

术语dBFS / Hz意味着噪声是以功率单位(dB)为单位定义的,相对于在1 Hz的频率分档宽度内看到的ADC满量程。1赫兹,你可能会问?为什么这么小?1 Hz是噪声带宽的基准单位,它建立了一个频率范围内观测箱的宽度用于定义NSD的宽度。

对于绝对参考,NSD也可以由ADC输入功率以dBm / Hz的绝对值来定义。在这种情况下,ADC的绝对满量程输入功率必须是已知的或基于输入电压和阻抗进行测量。

NSD规范如何帮助我区分适用于我系统的ADC?

随着奈奎斯特速率ADC的采样频率加倍,噪声密度分别下降3 dB,因为它分布在更宽的奈奎斯特频带上。对于2倍采样率,相同量的输入噪声功率现在将分配给两倍带宽,这增加了SNR。这可以通过在以下公式中将采样频率(fs)的值加倍来实现-3 dB降低来验证:

随着高速ADC的采样率继续增加到GHz范围,可以实现由于过采样而提高SNR的好处。在比较两个ADC的性能指标时,可以考虑采用较高频率采样的可能性以及较低的噪声密度。

NSD与我的快速傅里叶变换(FFT)的本底噪声有什么不同?

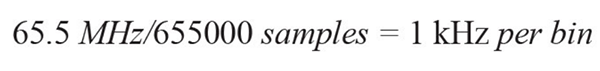

典型的FFT采用数十或数十万个采样点 - 甚至可能是几百万个采样点。对于大多数ADC采样率,这意味着bin频率大小代表数百Hz或几kHz的范围。FFT bin大小被定义为奈奎斯特频谱(fs / 2)除以具有频率单位的FFT采样的数量。例如,一个带有2 16(65.5 MHz)采样FFT 的131 MSPS ADC 的bin大小为:

因此,ADC的噪声以相对较大的箱体宽度分布在尼奎斯特区域,箱体宽度为NSD内定义的箱体宽度的1000倍。这包括在单个FFT箱中的更多噪声能量。

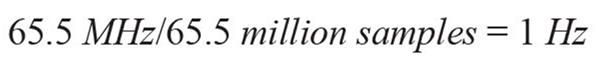

对于上面的示例,如果现在要为我们的131 MSPS ADC使用非常大的65.5 MS FFT,则箱宽将为:

在这种情况下,FFT的噪底将等于ADC的噪声谱密度,但总噪声功率仍然没有改变。如图1所示,相同的噪声功率只能在较宽的频率分档宽度上传播。

将其与NSD定义相比较,该定义具有带宽的噪声单位或1Hz的FFT分档频率大小。现在您可以了解为什么典型的FFT本底噪声几乎总是高于噪声谱密度。很少有工程师在系统中使用足够大的FFT大小来实现仅1 Hz的箱宽。这就是为什么当FFT中的采样数量增加时,噪声似乎变得更低。

但是,总的噪音并没有改变。它仍然在同一奈奎斯特频谱上传播。NSD定义不是使用由样本大小定义的频率仓增量,而是使用较小的1 Hz频率仓增量,将较少的噪音能量捕获到一个仓中。

如何测量和计算NSD?

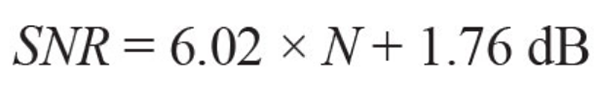

对于理想的ADC:

其中N是ADC的分辨率,这将定义ADC的量化噪声电平。真正的ADC不会达到这些性能指标,因为其设计中的非线性会将其实际SNR限制在理想范围内。换一种方式,如果我们从ADC的满量程输入功率中减去信号功率,其余的就是总噪声功率。如果我们从我们的国民生产总值数字中总结所有1赫兹的噪音箱,我们将得到一个单一的功率噪音数。

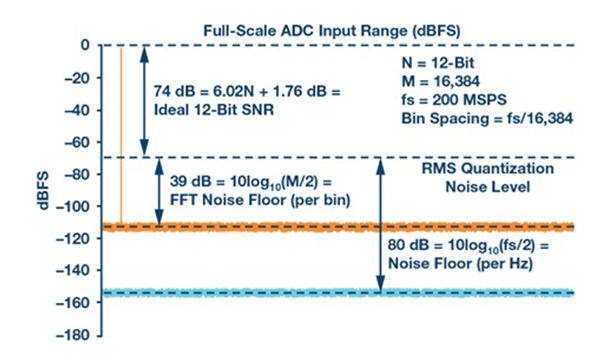

为了确定奈奎斯特速率ADC的NSD值,必须计算噪声如何在奈奎斯特区域内扩散的计算,并从满量程信号功率中减去。首先,我们必须知道采样率。我们来看一个理想的12位,200 MSPS ADC,它具有理想的满量程信号:

其噪声分布在100 MHz奈奎斯特区(fs / 2)。可以使用对数函数计算每1赫兹的噪声

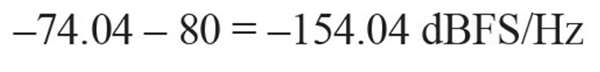

对于这个12位理想转换器,NSD将是:

由于我们生活在具有非理想ADC的非理想世界中,因此我们必须找到ADC的实际SNRFS。这可以直接测量,也可以从制造商的数据表中提取。

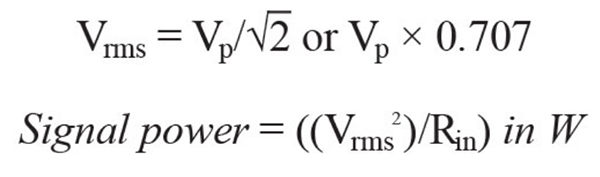

ADC的满量程输入信号功率电平是使用已知的满量程峰值电压或满量程均方根电压和ADC的输入电阻来计算的。如果输入电压和输入阻抗已知,我们可以以dBm为单位计算满量程功率,其中:

对于以dVm为单位的满量程信号功率:

ADC的量化噪声频谱的形状是什么?它总是平坦吗?

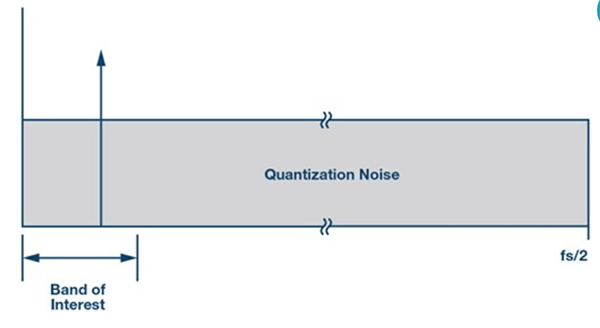

奈奎斯特速率ADC工作在捕获有关整个输入带宽的所有信息所需的最小采样频率。大多数采用流水线,逐次逼近寄存器(SAR)或闪存类型架构的奈奎斯特速率ADC的量化噪声从直流到奈奎斯特频率基本上是平坦的。因此,它们将是平等机会噪声接收机,并在整个fs / 2频谱上均匀接收有限功率量化噪声,如图2所示。

对于不需要完整奈奎斯特带宽的应用,可以实现备用ADC架构。带通连续时间Σ-Δ(CTΣΔ或CTSD)ADC使用噪声整形功能,该功能主要将带内量化噪声推出或滤波到感兴趣的频带外(图3)。这会导致噪声传递函数具有非平坦形状,该形状在窄带感兴趣区域中被降低,小于奈奎斯特带宽。在这个频段中,CTSD ADC在SNRFS最高时运行到最高性能,如图4所示。

由于CTSD架构的主要优点之一是它能够在窄频带内检测信号,因此宽带NSD并不特别令人感兴趣。相反,窄通带内的动态范围将突出显示为CTSD ADC的性能指标。噪声整形传递函数将根据调制器设计中使用的环路滤波器顺序来确定。

ADC的处理增益如何影响噪声密度和SNR?

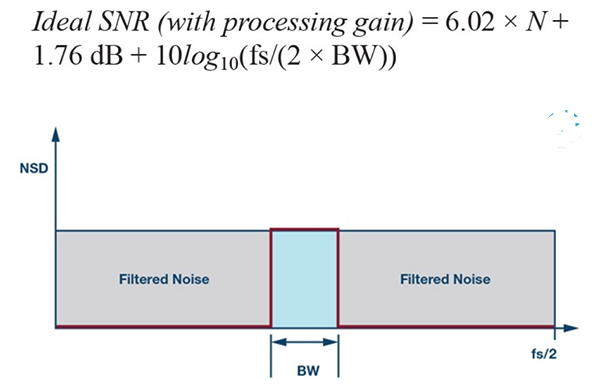

有几种应用,感兴趣的主要信号只位于一个很小的带宽内,远小于完整的奈奎斯特带宽。在这种情况下,数字滤波可用于滤除较小带宽之外的噪声。可以使用数字下变频阶段完成这一处理,在数据从奈奎斯特速率ADC输出之前对数据进行抽取,调谐和滤波。然后,我们的SNR计算必须包含此滤波的校正因子,以考虑滤波后噪声的处理增益,如图5所示:

假设我们使用采样频率为100 MSPS的奈奎斯特速率ADC,但是,我们的系统应用程序不需要观察转换器的整个50 MHz奈奎斯特带宽。相反,我们只希望在6.25 MHz的带宽部分(20 MHz和26.25 MHz之间)观察到较小的Nyquist的1/8。如果我们实施数字滤波算法并将滤波器调谐到这个感兴趣的带宽,则可以计算由于过采样造成的9 dB的处理增益:

对于每两次带宽减少的功率,由滤波后的噪声引起的处理增益将增加3dB。在上面的例子中可以看到,带宽减少1/23,可以产生3 dB×3dB的处理增益。

其他配套组件可以影响我系统中ADC的NSD性能?

许多外部因素会降低高速ADC的最佳性能。这可能导致较低的信噪比和较高的有效噪声密度。任何影响ADC的SNRFS或采样率的互补组件都有可能影响系统中的NSD。让我们关注时钟抖动,这是ADC采样频率较高时常见的SNR降级原因之一。

高速,高分辨率ADC对时钟输入的质量非常敏感。要在高速ADC中实现卓越的SNR,必须根据应用输入频率的要求仔细考虑均方根(rms)时钟抖动。均方根时钟抖动可能会限制性能最佳的ADC的信噪比,在更高的输入频率下加剧。虽然这不会改变ADC的NSD电位,但会在具有高抖动时钟的系统中限制其实际SNR性能。

由于ADC的模拟输入频率使用相同的rms时钟抖动三倍,所以最佳SNR性能降低了10 dB。给定输入频率(fA)下仅由于孔径抖动(tJ)引起的SNR的降级可通过以下公式计算:

图6显示了以飞秒为单位的不同均方根时钟抖动曲线的各种输入频率的SNR限制性能。随着输入频率的增加,需要较低的rms时钟抖动来实现相同的SNR限制,如在较低的输入频率下所见。例如,200飞秒的均方根时钟抖动将ADC的SNR性能限制在250 MHz时不超过70 dB。然而,1 GHz输入信号需要50飞秒或更好的rms时钟抖动才能达到70 dB的相同SNR性能。

ADC的噪声频谱密度可以很容易地定义为ADC的满量程信号功率减去噪声功率,分布在1 Hz带宽单位增量上。FFT采样深度的变化不会改变ADC的频谱噪声密度。它只在不同频率的单位带宽上传播噪声。

噪声形状可以根据ADC架构以及是否使用数字滤波来过滤带外噪声而有所不同。对于奈奎斯特速率ADC而言,处理增益可以增强感兴趣带宽内的动态范围,奈奎斯特速率ADC具有比系统所需的更宽的带宽。

作者:伊恩海狸

Ian Beavers是位于北卡罗来纳州格林斯博罗的模拟器件公司的高速模数转换器团队的应用工程师。他从1999年起为该公司工作。他在半导体行业拥有超过18年的经验。他还拥有北卡罗来纳州立大学电气工程学士学位和北卡罗来纳州格林斯伯勒大学工商管理硕士学位。他是EngineerZone®高速ADC支持社区的成员。欢迎将您的问题发送给Analog Devices EngineerZone在线技术支持社区的IanB。