IC放大器用户指南:去耦、接地及其他一些要点

selina -- 周三, 04/17/2019 - 10:53

作为讨论多数人受其禺弄的问题的开场白,这句话似乎再适合不过。我们为系统功耗、接地及信号回路找合适配置的时候,往往会引入一些干扰。然而严格的实验方法可以用来解决简单的问题,预见性通常也要以避免出现严重问题,并能在将来做一些补救措施。

作为讨论多数人受其禺弄的问题的开场白,这句话似乎再适合不过。我们为系统功耗、接地及信号回路找合适配置的时候,往往会引入一些干扰。然而严格的实验方法可以用来解决简单的问题,预见性通常也要以避免出现严重问题,并能在将来做一些补救措施。

作者:Paul Brokaw

作为讨论多数人受其愚弄的问题的开场白,这句话似乎有适合不过。我们为系统功耗、接地及信号回路找合适配置的时候,往往会引入一些干扰。然而严格的实验方法可以用来解决简单的问题,预见性通常也可以出现严重问题,并能在将来做一些补救措施。

作者:Walt Kester

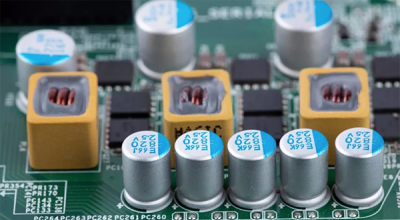

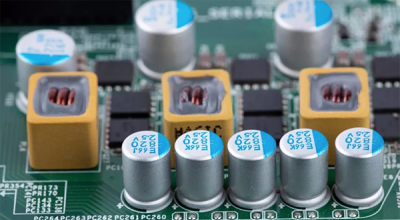

在上篇文章中,我们介绍了去耦的基础知识及其在实现集成电路(IC)期望性能方面的重要性。在本篇文章中,我们将详细探讨用于去耦的基本电路元件——电容。

实际电容及其寄生效应

何谓正确去耦?有何必要性?

如果电源引脚上存在纹波和/或噪声,大多数IC都会有某种类型的性能下降。数字IC的噪声裕量会降低,时钟抖动则可能增加。对于高性能数字IC,例如微处理器和FPGA,电源额定容差(例如±5%)包含直流误差、纹波和噪声之和。只要电压保持在容差内,数字器件便符合规范。