ADI公司新型Easy Drive™ SAR ADC可简化设计并提供领先的性能

winniewei -- 周四, 05/05/2022 - 10:12

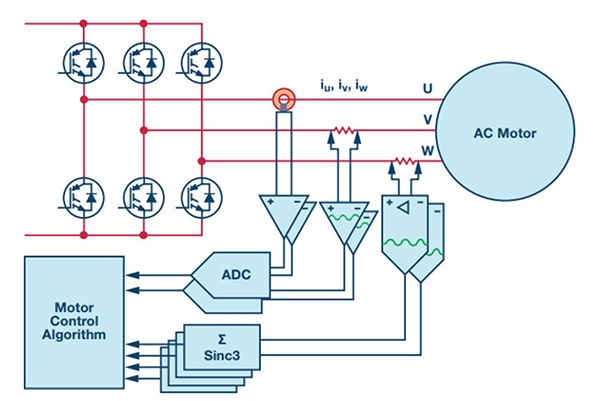

Ʃ-Δ 型模数转换器广泛用于需要高信号完整度和电气隔离的电机驱动应用。虽然Σ-Δ技术本身已广为人知,但转换器使用常常存在不足,无法释放这种技术的全部潜力。本文从应用角度考察Σ-Δ ADC,并讨论如何在电机驱动中实现最佳性能。

在三相电机驱动中测量隔离相电流时,有多种技术可供选择。图1显示了三种常用方法:一是隔离传感器(如霍尔效应或电流互感器)结合一个放大器;二是电阻分流器结合一个隔离放大器;三是电阻分流器结合一个隔离Σ-Δ ADC。

本文重点讨论性能最高的方法——Σ-Δ转换。通常,Σ-Δ ADC针对的是需要高信号质量和电流隔离度的变频电机驱动和伺服应用。随ADC而来的还有解调和滤波,这些一般是由FIR滤波器(如三阶sinc滤波器sinc3)处理。

作者:Miguel Usach Merino和Gerard Mora-Puchalt

ADI 专利的容性可编程增益放大器(PGA)相比传统的阻性PGA具有更佳的性能,包括针对模拟输入信号的更高共模电压抑制能力。

新的国际标准和法规加速了工业设备对安全系统的需求。功能安全的目标是保护人员和财产免受损害。这可以通过使用针对特定危险的安全功能来实现。安全功能由一系列子系统组成,包括传感器、逻辑和输出模块,因而需要系统层面和集成电路层面的专门技能来提供具有适当功能组合的IC。

墨菲定律变体之一:"如果几件事都可能出错,首先出错的往往是会造成最大损失的那一件。"

如果一个系统可能产生直接或间接的致命威胁,例如机器故障等,那么设计该系统时,必须最大程度地降低故障可能性及其导致的负面影响。为了确保发生随机性和确定性故障的概率尽可能低,必须遵循特定的设计方法。工业中将这种设计方法称为功能安全方法。这种方法要求对系统进行细致入微的分析,确定所有潜在的危险情况,并运用最佳做法来将器件、子系统和系统的故障风险(例如电压过高或诊断失败等)降至容许的水平。

功能安全背后的理念是当检测到错误时让系统保持安全状态,例如:若来自外部传感器的转换结果超出范围,则断开使能的输出连接。IEC-61508是工业设备功能安全设计参考标准,已针对不同行业进行了修改或阐释,例如ISO-26262适用于汽车行业,IEC-61131-6适用于可编程控制器。

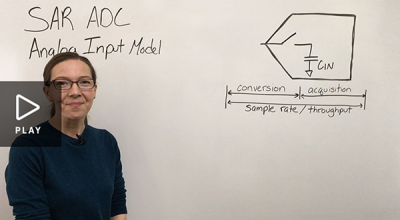

了解SAR ADC反冲建立的要求和RC滤波器元件的计算。

介绍SAR ADC反冲幅度和时间常数公式。

SAR(逐次逼近寄存器)ADC模拟输入模型、反冲和RC滤波器简介。

功能安全是诸多行业整体安全策略的一部分,其目的是将对人或作业设备造成伤害的概率降至可接受的范围以内。近年来,人们对系统功能安全的要求显著增长。从核电站到医疗设备,无故障系统已成为部分应用的理想选择,也是其他应用的必备条件。例如,在传感领域,获取的数据如果不正确或遭到损坏,结果可能具有破坏性,甚至可能致命,具体取决于系统和所涉及的风险级别。

传统上,系统开发人员有责任将诊断和故障预防机制集成到其产品当中,确保来自传感IC的数据的完整性。但其代价是会增加PCB面积、物料成本和处理开销,最终会导致费用增加。从那时起,通过与系统设计工程师的广泛合作,人们开发出了一种解决方案来解决这个问题。为此,人们已经开始在IC级设计中考虑功能安全特性。

本文旨在从确保数据采集系统整体完整性的角度,探讨通过ADC实现功能安全的潜力。C 级设计中考虑功能安全特性。

传统的功能安全解决方案与更佳的方式

功能安全是诸多行业整体安全策略的一部分,其目的是将对人或作业设备造成伤害的概率降至可接受的范围以内。近年来,人们对系统功能安全的要求显著增长。从核电站到医疗设备,无故障系统已成为部分应用的理想选择,也是其他应用的必备条件。例如,在传感领域,获取的数据如果不正确或遭到损坏,结果可能具有破坏性,甚至可能致命,具体取决于系统和所涉及的风险级别。

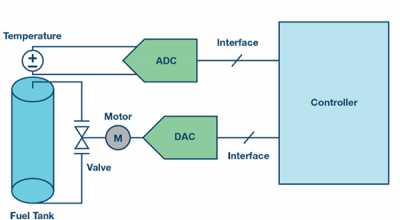

模数转换器(ADC)能够将模拟量转变成数字量,因此它是电学测量、控制领域中一个极为重要的部件。一般来说,一个模拟电压信号,在进入ADC的输入端之前,都需要增加一级驱动电路(Driver);但是也有一些ADC具有“极贴心设计”的输入端,这就无需在前级增加驱动电路了。那么到底什么时候该加,什么时候不该加呢?且听杨老师娓娓道来~

向下箭头分割线GIF动态

加或不加,都得从原理说起,毕竟原理才是学习模电的重点。首先我们要知道,为什么要给ADC前端增加驱动电路?杨老在这儿给出了5条理由,包括:

* 输入范围调整

* 输入类型转换

* 低阻输出,以减小测量误差

* 输入类型转换

* 抗混叠滤波

其中,只要有一条是必要的,就必须使用ADC驱动电路。下面进行一一分析。

输入范围调整

任何一个ADC,都有输入电压范围。当实际输入电压超出此范围,将引起ADC转换失效。而被转换的信号,并不能保证在此范围内,这就需要ADC驱动电路将其调整到合适的范围之内。

输入范围调整,包括对信号的增益改变,以及直流电平移位两个功能。

输入类型转换