了解并延续∑-Δ ADC的安全运行

selina -- 周五, 07/06/2018 - 14:36

作者:Miguel Usach Merino

摘要

作者:Miguel Usach Merino

摘要

作者:Barry Zhang 和 Alex Buda

简介

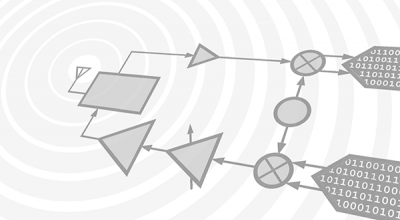

Analog Devices, Inc. (ADI)近日推出一款射频(RF)模数转换器(ADC),可实现业界领先的速度和带宽。与传统的射频ADC相比,新型AD9213具有更高的参数性能和更大的奈奎斯特带宽,并且能够在更高的模拟输入频率下进行射频采样,可实现高达7 GHz的射频信号的数字化。

摘要

ADI专利的容性可编程增益放大器(PGA)相比传统的阻性PGA具有更佳的性能,包括针对模拟输入信号的更高共模电压抑制能力。

本文描述了斩波容性放大器的工作原理,强调了需要放大传感器小信号至接近供电轨——比如温度测量(RTD或热电偶)和惠斯登电桥——时,此架构的优势。

简介

作者:Reza Moghimi,ADI公司应用工程经理

高精度应用需要精心设计的低噪声模拟前端来获得最佳信 噪比(SNR),这就要求采用明智的方法来选择ADC以全面 准确地捕捉传感器信号。还要选用驱动运算放大器和基准 电压源等支持器件来优化电路性能。

作者:Rui Du

简介

作者:Mary McCarthy和Eamonn Dillon

简介

在过去的几十年中,由于信号采集系统的不断增加和永不满足的带宽需求,尽管速度很慢,但高速模数转换器(ADC)性能指标发生了很大变化,尽管速度缓慢。ADC性能测量的方式也发生了变化。

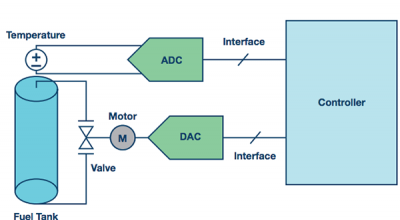

作为真实世界信号与现代数字信号处理功能电路之间的关键使能接口——精准模数转换器,广泛应用于工业过程中的高端测试/测量系统。

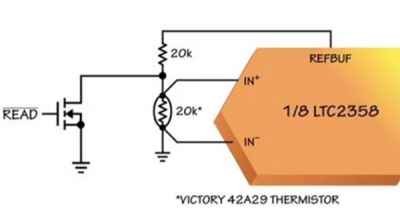

但是,想要把传感器或其它信号源连接至转换器并获得数据转换器产品广告中宣称的所有性能,并不是一件容易的事,通常还需要用于提供缓冲、电压保护或其他功能等附加电路的帮助。

那么,该如何简化这个问题呢?