作者:Alan Walsh 应用工程师 ADI公司

精密测量已延伸到需要越来越高电源效率的应用领域。物联网的到来使这一点尤为明显,因为物联网更加需要具有精密测量能力的无线传感器节点,电池供电的可穿戴健身/医疗设备,以及使用隔离电源供电、4 mA到20 mA环路供电或电池供电现场仪表的工业信号链。在这些场景中,电源效率越高,意味着电池使用时间越长,维护越少,电源设计越简单。

通常,精密测量系统将低压差稳压器(LDO)作为其电源方案的一部分,利用它来为精密ADC产生低噪声电源轨。然而,LDO的功率输出效率非常低下,大部分功率常常作为热量损失掉。本文讨论为精密逐次逼近型(SAR) ADC实现更高效率电源解决方案的途径。实现方法是在迟滞模式下使用超低功耗开关稳压器,并分析性能得失——包括通过某种方式来智能控制开关稳压器,使之与SAR转换同步,从而改善噪声性能。

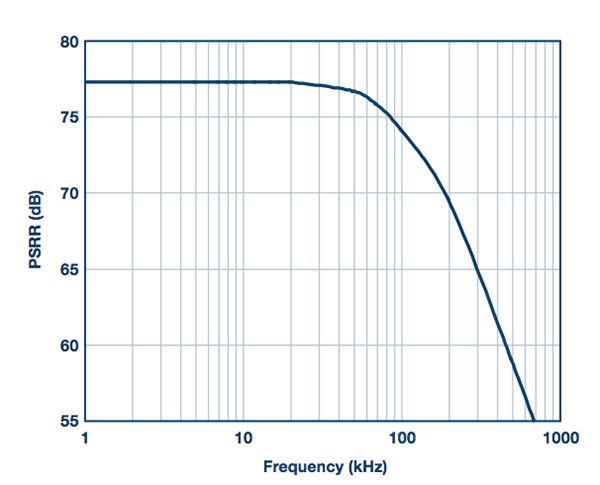

在中高负载电流(数百mA到数A)的测量系统中,固定频率或脉宽调制(PWM)开关稳压器可非常有效地(常常大于90%)产生电源轨。然而,效率虽然高,但代价是会有开关纹波,其频率通常是固定的,从数百kHz到数MHz。如图1所示,典型精密SAR ADC的电源抑制比(PSRR)在低频至约100 kHz时是非常好的——超过此频率时,PSRR迅速下降。

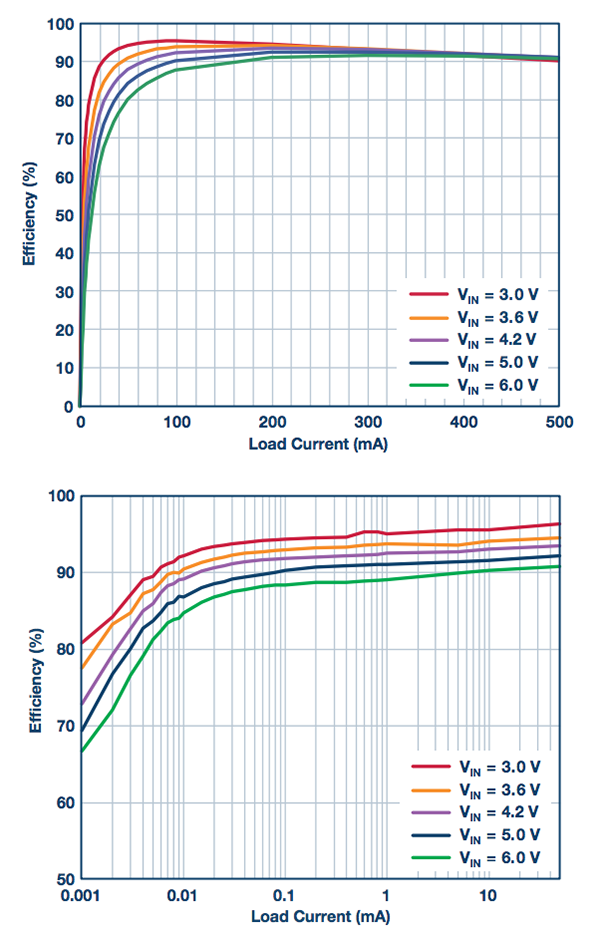

精密SAR ADC以较低吞吐速率运行时,供应VDD线的典型负载电流在数mA或µA范围——因此,相比于LDO,使用固定频率开关稳压器直接为ADC供电在效率上没有优势。然而,高效率、超低功耗降压开关稳压器可在迟滞模式下工作,其静态电流非常低。

在迟滞模式下,通过调节恒定峰值电感电流,稳压器利用PWM脉冲使输出电压略高于标称输出电压。当输出电压提高到输出检测信号超过迟滞上限时,稳压器进入待机模式。在待机模式下,高端和低端MOSFET及大部分电路都禁用,静态电流很低,效率性能很高,如图2所示。待机模式期间,输出电容将能量送入负载,输出电压降低到低于迟滞比较器下限为止。稳压器唤醒,产生PWM脉冲,再次对输出充电。

在迟滞情况下,开关纹波频率与负载电流和LC网络有关;对于数mA的负载,其在kHz范围内。在数kHz时,精密ADC的PSRR非常好,能够很好地抑制/衰减ADC数字输出端的开关纹波。

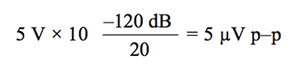

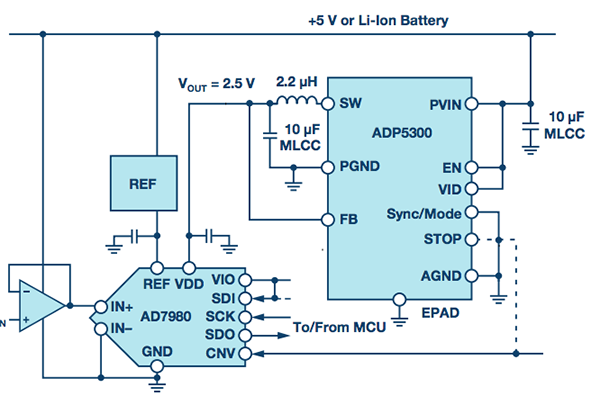

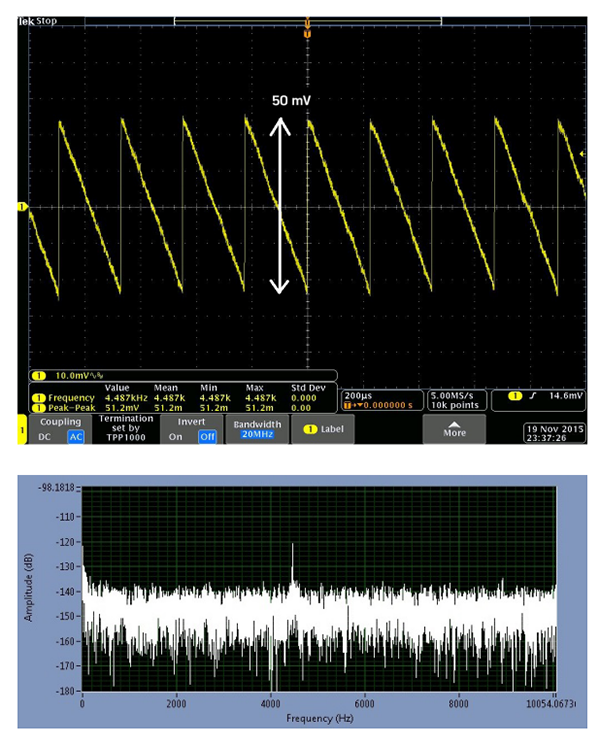

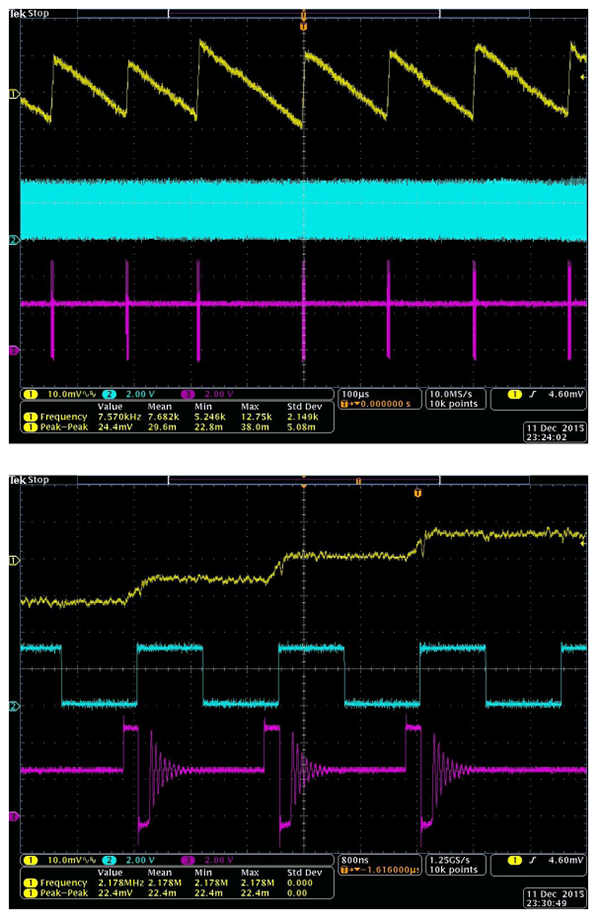

以图3所示电路为例,它使用AD7980ADC;在全吞吐速率(1 MSPS)时,其VDD电流消耗典型值为1.5 mA;若降低吞吐速率,电流消耗会按比例线性下降。这可从图4看出:采用5 V电压轨供电时,2.5 V稳压输出端的开关频率纹波为4.5 kHz和50 mV峰峰值。在ADC数字输出端,ADC以PSRR额定值衰减此纹波。在ADC FFT输出中,它表现为幅度−120 dBFS、频率4.5 kHz的杂散。对于ADC的5 V输入范围,这相当于

出现在ADC输出端的这种纹波水平对一个16位转换器而言是非常低的;5 μV峰峰值对应于16位下的0.07 LSB。这种水平的纹波会被埋在ADC噪底中,需要大量均值操作才能发现,在很多应用中都不会看到它。此输出纹波对应的PSRR为

该要求与图1所示相似,AD7980在4.5 kHz时的PSRR约为77 dB。

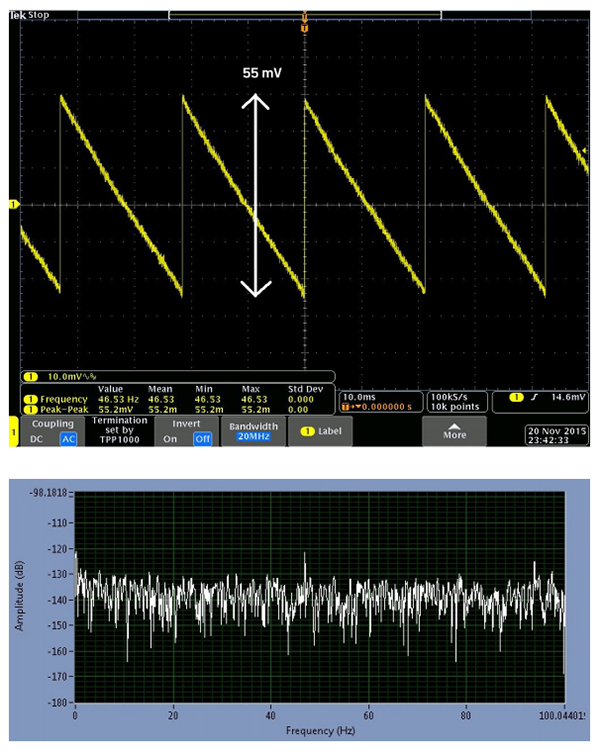

若ADC吞吐速率降低到10 kSPS,则ADC的电流消耗按比例线性下降到15 μA (约100倍),ADP5300 的开关频率纹波相应地降低到46.5 Hz (约100倍),幅度为55 mV峰峰值,如图5所示。在46 Hz时,该纹波再次在ADC FFT输出中出现,幅度为−120 dB (5 μV峰峰值),因为在该频率的PSRR相似。有证据表明存在93 Hz的二次谐波,其幅度更低,为−125 dB。

吐速率时的ADC FFT输出中的纹波音

图6对照显示了ADP5300和LDO在不同ADC吞吐速率时的效率,两种情况均采用5 V电压轨供电,调节2.5 V输出。同预期一样,开关稳压器输送功率的效率远胜于LDO,在1 MSPS时是90%对50%(针对5 V输入),在较低ADC吞吐速率/较低电流消耗时保持得也更好,始终高于80%,直至5 kSPS。ADC吞吐速率为1 MSPS且使用LDO时,从5 V电压轨消耗的电流为1.5 mA或7.5 mW。使用ADP5300时,从5 V电压轨消耗的电流为828 μA或4.1 mW,即ADC电源的功耗减少3.4 mW或45%。

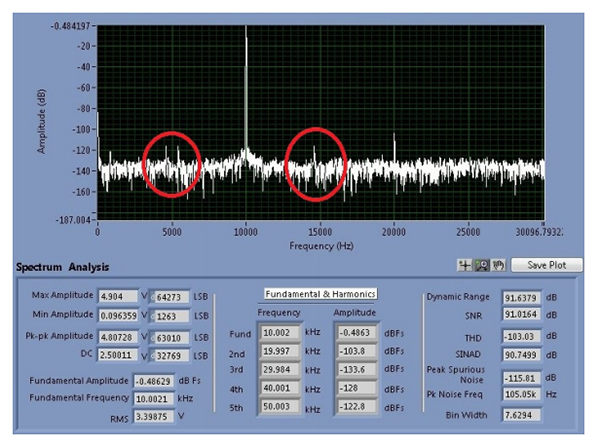

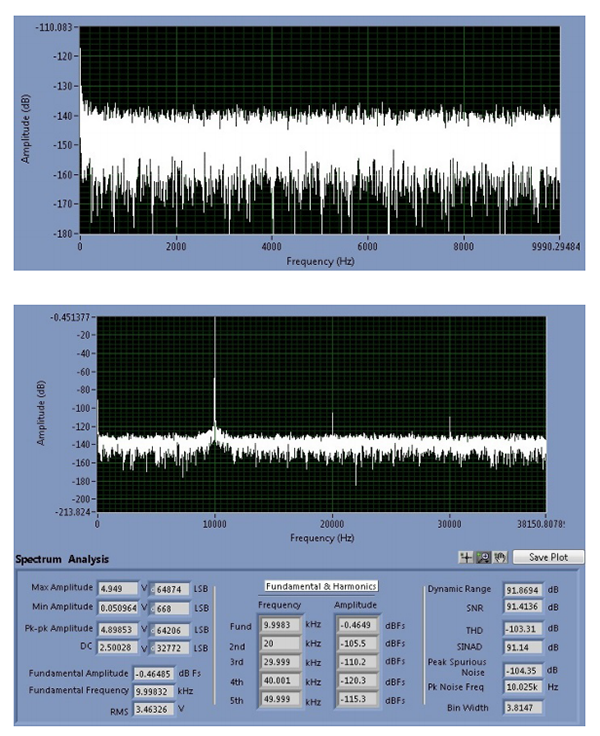

使用ADP5300作为VDD电源以及10 kHz近满量程输入信号(−0.5 dB),AD7980在1 MSPS时的性能如图7所示。在SNR (91.5 dB)和THD(−103 dB)方面,ADC仍然符合数据手册规格。然而,ADP5300的4.5 kHz开关纹波会在输入信号上进行调制,显示为10 kHz – 4.5 kHz(5.5 kHz)和10 kHz + 4.5 kHz (14.5 kHz)的杂散。这些杂散仍然处于非常低的水平(−116 dBFS),远小于基波信号的二次谐波引入的THD(其在20 kHz时为−103.8 dBFS)。在16位水平时,这些伪像只是一个LSB的很小一部分,因而在许多应用中,考虑到ADP5300稳压器的省电优势,这是完全可以接受的。

ADP5300开关稳压器有一个STOP (停止)切换特性,它可以完全消除开关纹波伪像,使其不会出现在ADC FFT输出中。当STOP处于高电平时,ADP5300的STOP引脚就会阻止SW引脚切换。在对噪声敏感的ADC转换过程中,可利用该特性防止切换发生。为实现这一功能,CNV信号和STOP信号应连在一起(参见图3),并且对来自处理器的CNV信号进行定时,使其在ADC转换时保持高电平。对于AD7980,此时间最大值为710 ns,转换在CNV上升沿启动。结果如图8所示。这种情况下的纹波频率更加变化不定,因为只有在特定时间,SW节点才会开启和调节。另请注意,从STOP信号变为低电平到SW开启的时间可能为数百ns。图8中,STOP下降沿后大约850 ns,SW引脚开启。这意味着,当ADC吞吐速率为1 MSPS时,我们不能使用STOP特性,因为SW引脚将没有足够的时间来变为高电平并调节,VDD电源将失去调节而崩溃。STOP功能在吞吐速率为500 kSPS或更低时有效。

从图9可以看出,使用STOP信号后,ADC噪底中完全不存在开关纹波杂散。当施加10 kHz的输入信号时,除一般谐波之外,基波周围没有调制。然而,当SW引脚禁用(STOP为高电平)时,由于SW引脚上的振铃,使用STOP特性的效率会下降。对于500 kHz的ADC吞吐速率,ADP5300的效率降至约75%。这仍然显著高于LDO能够实现的效率(<50%),并且提供了一个功耗/性能权衡选择;在受处理器/微控制器控制且STOP特性使用独立控制线的应用中,就可以做出适当的权衡。

ADP5300等开关稳压器解决方案与LDO解决方案在成本和PCB面积方面具有一定的可比性。BOM主要增加一个电感,2.2 μH电感可以小到0603封装,而对于输入和输出电容,LDO解决方案同样需要。因此,在功耗敏感型应用中,它是LDO的有力替代方案,对精度性能并无明显影响。

当从5 V电源轨为AD7980等精密ADC供电时,ADP5300等高效率、超低功耗开关稳压器与LDO相比,可节省45%的功耗。这对物联网应用(延长无线传感器节点或可穿戴设备的电池使用寿命)、功耗敏感型隔离式工业系统、4 mA至20 mA环路供电系统有很多好处。

作者简介

Alan Walsh [alan.walsh@analog.com] 是ADI公司的应用工程师。他于1999年加入ADI公司,就职于美国马萨诸塞州威明顿市的精密转换器应用部。他拥有都柏林大学电子工程学士学位。