摘要

数据转换器是通信系统中的重要元件,构成模拟传输媒介(如光纤、微波、射频和FPGA及DSP等数字处理模块)之间的桥梁。系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。目前市场上有性能属性大相径庭的众多时钟发生器。然而,如果不慎重考虑时钟发生器、相位噪声和抖动性能,数据转换器、动态范围和线性度性能可能受到严重的影响。本文将详细讨论时钟发生器、相位噪声和抖动对数据转换器(ADC和DAC)的动态范围和线性度的影响。文中将就时钟抖动对转换器SNR的影响进行理论分析,同时介绍运用ADI高性能时钟发生器得到的仿真结果。

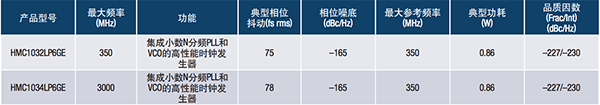

ADI开发了一个独特的高性能时钟分配和时钟发生产品系统,使系统设计师可以实现数据转换器的最佳性能。HMC1032LP6GE和HMC1034LP6GE为SMT封装时钟发生器,是多种高性能蜂窝/4G基础设施、光纤和网络应用的理想选择,在同类产品中具有最佳的抖动性能和行业领先的相位噪底。HMC987LP5E 1:9扇出缓冲器是关键应用中充当时钟驱动器的最佳选择,噪底超低,仅−166 dBc/Hz。这些器件的主要技术规格如表1和表2所示。

系统考虑因素

采用MIMO (多输入多输出)架构的典型LTE (长期演进)基站如图1所示。该架构由多个发射器、接收器和DPD (数字预失真)反馈路径构成。各种发射器/接收器组件(如数据转换器(ADC/DAC))和本振(LO)要求采用低抖动参考时钟以提高性能。其他基带组件也要求各种频率的时钟源。

表1.时钟发生器——典型性能

表2.时钟分配产品——典型性能