作者:电子创新网张国斌

在人工智能时代,计算需求急剧增加,芯片的晶体管数量不断攀升,GPU(图形处理单元)芯片在未来可能需要包含上万亿个晶体管。这一目标的实现离不开先进封装技术的支持,在第十六届集成电路封测产业链创新发展论坛同期召开的芯片设计与先进封装技术专题论坛上,芜湖立德智兴半导体有限公司CTO 李元雄人分享了万亿晶体管的GPU芯片如何通过先进封装技术实现,并展望了未来发展方向。

李元雄指出人工智能的发展依赖于算法、算力和数据三个基石。随着算法的复杂性和数据量的增加,计算能力的提升变得至关重要。从1960年代集成电路发明至今,算力增长了千亿倍,相当于接近人脑的计算能力。未来的人工智能应用,如实时语音对话、自动驾驶和智能翻译等,都需要极高的计算能力,这推动了对万亿晶体管芯片的需求。

|万亿晶体管的芯片设计

他表示i要实现万亿晶体管的集成,关键在于垂直堆叠(3D)和水平扩展(2D、2.5D)两种方法。垂直堆叠通过增加芯片层数来提升集成度,水平扩展通过扩大芯片的面积来容纳更多的晶体管。

目前主要采用的先进封装技术有:

1、Foveros技术:英特尔的Foveros技术使用有源转接板,实现芯片的三维堆叠,通过XY和Z轴的延伸,增加互连密度。

2、SoIC技术:台积电的SoIC技术取消了凸点,通过混合键合技术提高了堆叠效率,互连密度达到了每平方毫米100万个连接点。

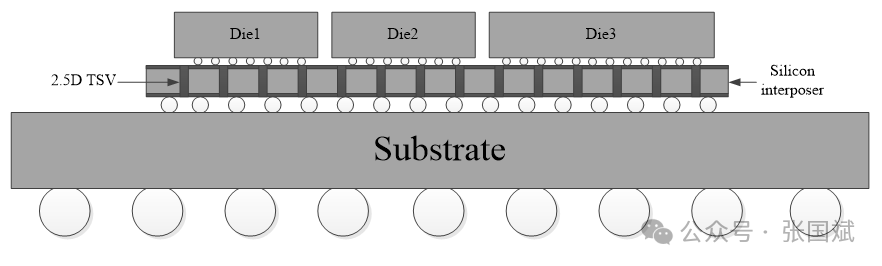

3、CoWoS技术:(Chip-on-Wafer-on-Substrate)是台积电推出的 2.5D封装技术,CoWoS是把芯片封装到硅转接板(中介层)上,并使用硅转接板上的高密度布线进行互连,然后再安装在封装基板上,如下图所示。

CoWoS主要用于高性能计算的2.5D封装技术,将多个芯片集成在一个硅中介层上,适用于高端GPU芯片。

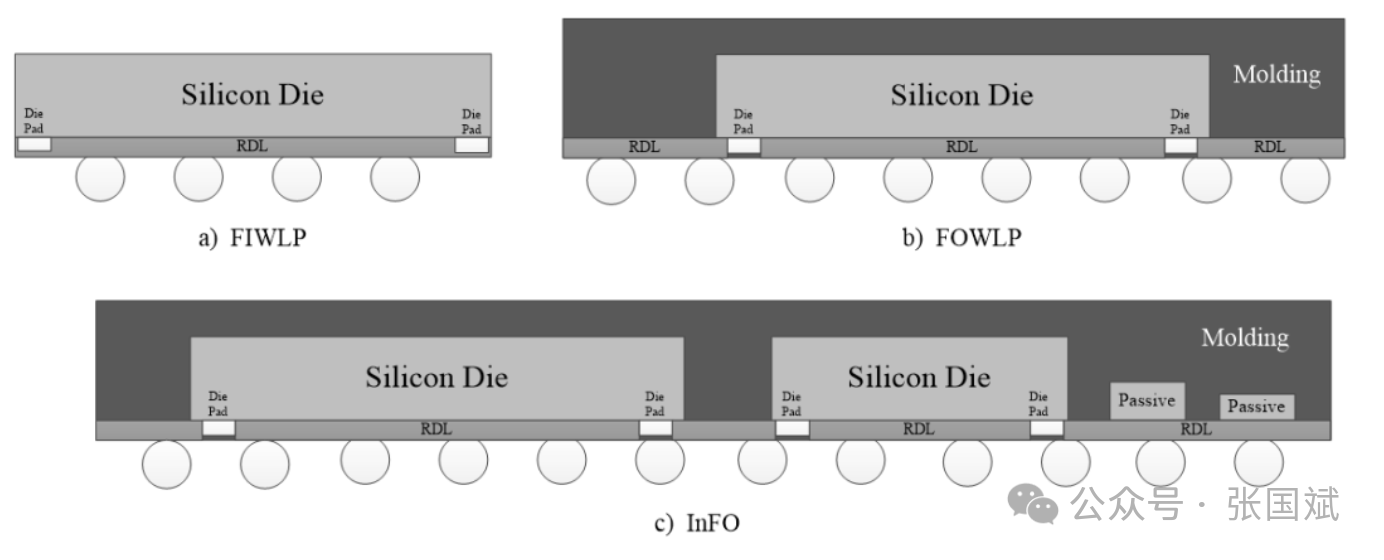

4、InFO技术:集成扇出型封装技术,是台积电(TSMC)于2017年开发出来的FOWLP先进封装技术,是在FOWLP工艺上的集成,可以理解为多个芯片Fan-Out工艺的集成 ,而FOWLP则偏重于Fan-Out封装工艺本身。

InFO给予了多个芯片集成的空间,可应用于射频和无线芯片的封装,处理器和基带芯片封装,图形处理器和网络芯片的封装。下图为FIWLP,FOWLP和InFO对比示意图。

InFO是较经济的封装技术,适用于消费电子产品,通过无硅中介层的封装方式降低成本。

李元雄指出先进封装技术的实现依赖于高密度硅通孔(TSV)和高精度纳米级混合键合(Hybrid Bonding)等关键技术。TSV通过等离子刻蚀实现高密度互连,混合键合则通过铜柱和二氧化硅界面的键合,保证芯片的高效堆叠和互连。此外,2.5D封装的Interposer工艺流程相对简单,但需要精密的制造技术以保证芯片的可靠性和性能。

|经济高效的封装技术--扇出型晶圆级封装

李元雄特别指出扇出型晶圆级封装(Fan-out WLP)通过重构晶圆实现芯片的高效排列和封装,是一种适合本土芯片采用的经济高效封装方法。

扇出型晶圆级封装封装技术具有以下几方面的优势:

1. 高密度和小尺寸

扇出型封装可以实现高密度的互连,不需要中介层(如硅中介层),这使得其互连密度高于传统的封装技术。此外,扇出型封装可以显著减小封装后的芯片尺寸,因为它不需要在芯片周围保留过多的引脚或连接区域。这对于小型化和集成化要求高的现代电子产品非常重要。

2. 优秀的电性能和热性能

由于扇出型封装中互连线的长度较短,可以有效降低电感和电阻,从而提高电性能。这对于高频、高速信号传输尤为重要。此外,扇出型封装能够更好地散热,因为芯片和封装基板之间的热阻较低,有助于提升整体的热管理性能。

3. 成本效益

与传统的2.5D和3D封装技术相比,扇出型封装不需要昂贵的中介层和复杂的制造工艺,因此在成本上具有优势。特别是对于大规模生产的消费类电子产品,扇出型封装提供了经济高效的解决方案。

4. 高集成度

扇出型封装技术支持多个芯片的集成,可以将不同功能的芯片(如处理器、存储器、传感器等)集成在一个封装中,形成系统级封装(SiP),提高了系统的集成度和功能多样性。

5. 灵活性和设计自由度

他还补充说扇出型封装在设计上具有较大的自由度,可以根据具体需求调整芯片的位置和互连方式,从而优化封装的性能和功能。另外该技术可以通过增加芯片数量和调整封装布局,轻松扩展系统的性能和功能,满足不同应用场景的需求。

6. 可靠性

由于扇出型封装减少了机械应力和热膨胀系数的差异,提升了封装的可靠性和长期稳定性。特别是在移动设备和消费电子产品中,这种高可靠性尤为重要。

|立德智兴在扇出型晶圆级封装上的创新

李元雄表示芜湖立德智兴半导体在实现扇出型晶圆级封装技术上进行了多项创新,主要的创新亮点是:

1. 重构晶圆工艺(RW工艺)

据他介绍芜湖立德智兴半导体开发了一种关键设备,用于实现重构晶圆(Reconstituted Wafer)的工艺步骤。该设备能够在临时晶圆上覆盖一层膜,并按照特定规则重新排列芯片。重构晶圆工艺包括塑封、去除临时晶圆、在塑封原片上布线和Bump,最后进行切割。这种工艺非常简洁、高效且成本较低。

2. 自动光学检测和红外检测

此外,为了确保芯片的高可靠性,芜湖立德智兴半导体与华天科技合作开发了一种包含自动光学检测和红外检测功能的设备。传统的光学检测只能看到可见光下的缺陷,而红外检测可以发现普通光学检测无法察觉的隐裂。这种检测对于保证芯片的长期可靠性至关重要。

3. 高精度设备开发

另外,芜湖立德智兴半导体开发了专门的设备,能够在高度洁净的环境(如Class 10级的洁净室)中工作。这些设备不仅能自动化处理芯片的分选和放置(Pick and Place),还集成了六面自动光学检测功能,能够高效且精准地处理每小时5K到10K的芯片。

4. 八爪鱼旋转机构

为提高分选和放置的效率,芜湖立德智兴半导体开发了八爪鱼旋转机构。该机构每个爪子转30度即可抓取一个芯片,而不是传统的每次只抓一个芯片来回摆动。这大大提高了处理速度和效率。

5. 高效空气流通设计

为了减少设备运动部件产生的灰尘和颗粒,芜湖立德智兴半导体在设备设计上注重空气流通的优化,将运动部件尽量包裹起来,并设计了高效的灰尘去除系统。这些设计确保了设备在高洁净环境中的可靠运行。

通过这些创新,芜湖立德智兴半导体在扇出型晶圆级封装技术上取得了显著进展,为高性能和高可靠性的芯片制造提供了坚实的技术支持。这些技术不仅提高了封装效率,还降低了成本,为广泛应用于消费电子和高性能计算领域提供了可能性。

李元雄指出随着半导体工艺演进到2nm甚至1.6nm以及更高级工艺,传统 单芯片封测已经面临巨大的挑战,需要先进封装来延续半导体未来发展,他认为未来的先进封装要“集成一切IOA”!把包括硅器件、传感器、执行器、无源器件、光电子器件、量子器件在内的器件都以先进封装的手段集成在一起,这就是我们超越摩尔定律的不二选择。

“本来封装领域中国与世界的差距就小,我们的长电、华天、通富、华进全部在先进封装上进入了国内领先甚至是国际同行先进的行列,所以这对中国来说是一个绝好的换道超车的机会!”他总结说。

注:本文为原创文章,未经作者授权严禁转载或部分摘录切割使用,否则我们将保留侵权追诉的权利