ADI 的时钟芯片主要是 AD95xx 系列,用于合成频率,提供低抖动的时钟信号;ADCLK9xx 系列为时钟 Buffer,用于时钟分配,在低附加抖动的条件下提供多路 LVDS,LVPECL 等时钟驱动。

原理

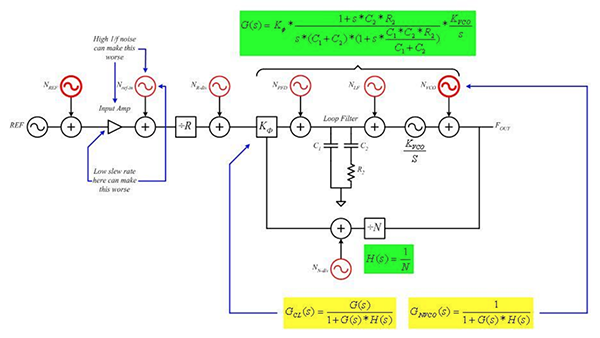

电子系统的心脏是时钟链路。时钟的原理和基础是锁相环和 DDS。时钟通过频率合成,提供所需要的频率、电平驱动、时钟同步等功能。相位噪声和抖动特性是时钟输出信号最重要和最基本的参数。锁相环的各个组成部分,包括参考源、参考分频、鉴相器、环路滤波器、压控振荡器等都对最终 PLL 的输出贡献噪声。如下图所示。传输函数决定了各个部分噪声的传输特性。

环路的传输函数、VCO 处噪声的传输函数、参考源噪声的传输函数可推导得到下面的等式。可以看出,VCO 的相位噪声是高通特性,参考源的噪声是低通特性。