作者:George Alexandrov 和 Nathan Carter

简介

用于光电二极管、压电以及其他仪器仪表应用的低噪声放大器所要求的电路参数一般是:极高的输入阻抗、低 1/f 噪声或亚皮安偏置电流等,而提供的集成产品无法满足这些要求。本文讨论使用分立元器件设计低噪声放大器的要求与挑战,并重点探讨了折合到输入的噪声以及失调电压调节。

高输入增益拓扑的限制

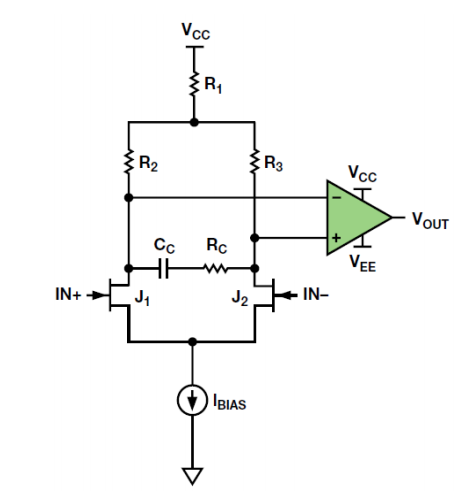

典型分立式放大器如图 1 所示,在高速运算放大器前使用匹配JFET 器件实现的差分放大器,提供高输入阻抗和一定的初始增益。系统噪声主要由输入级产生,因此无需使用低噪声运算放大器。

不过,将输出稳定在低增益和高频率有一定难度。添加 RC 补偿网络、CC和 RC后,即可实现稳定性,但这些元器件的最优值随增益而改变,增加了整体设计的复杂性。另外,大信号响应对于某些应用而言也过于缓慢。

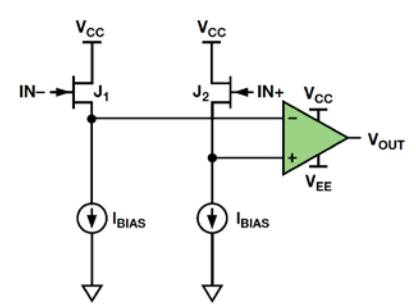

图 2 所示电路在单位增益处可获得相应的噪声性能,无需进行补偿。速度主要由运算放大器确定。该电路由三个主要部分组成:输出运算放大器、FET 输入缓冲器以及对 FET 进行偏置的电流源。