作者:Rob Reeder

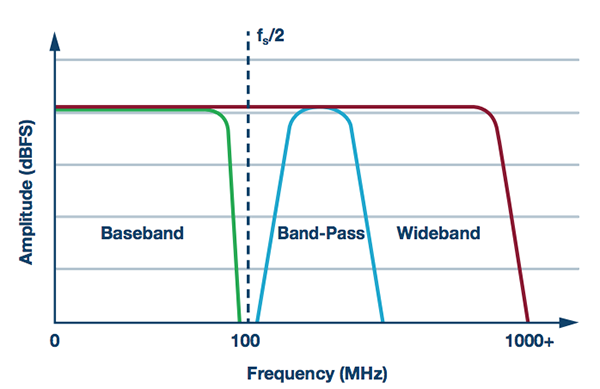

有很多令人困惑的规格都与转换器带宽有关。为了在新的设计中选用适当的转换器,我应当使用什么带宽术语呢?开始一个新设计时,需要决定的首要参数就是带宽。带宽为设计指明方向,引导设计人员开辟通往成功之路。本质上有三类前端可供选择:基带型、带通或超奈奎斯特型(有时也称为窄带或子采样型——基本上不会用到第1奈奎斯特区)以及宽带型,如图1所示。前端的选用取决于具体应用。

基带设计要求的带宽是从直流(或低kHz/MHz区)到转换器的奈奎斯特频率。用相对带宽表示的话,这意味着大约100 MHz或以下,假定采样速率为200 MSPS。这类设计可以采用放大器或变压器/巴伦。

带通设计意味着在高中频时只会使用转换器带宽的一小部分(即小于奈奎斯特频率)。例如,还是假定采样速率为200 MSPS,可能只需要20-60MHz带宽,以170 MHz为中心。不过,随着新一代GSPS转换器类型产品的发布,市场呈现出向更高中频发展的趋势。因此,上述示例中的数值可能会多填充一个0。本质上讲,设计人员只需利用转换器带宽的一小部分就能完成工作。这种设计通常使用变压器或巴伦。不过,如果较高频率下的动态性能足够并且需要增益,也可以使用放大器。

宽带设计通常指需要全部带宽的设计。转换器能够提供多少带宽,用户就会使用多少带宽——供大于求!在三种设计中,这种设计的带宽最宽,因而是最具挑战性的前端设计。如果设计要求整个通带的平坦度为0.1dB,则更具挑战性。这类应用的带宽范围为直流或低kHz/MHz区至+GHz区。此类设计常常采用宽带巴伦耦合到转换器。

关于带宽的说明

术语“带宽”在工程领域中遭到滥用,根据应用的不同,带宽的含义在不同设计人员看来可能完全不同。在本文中,转换器的全功率带宽与转换器的可用带宽或采样带宽是不同的。全功率带宽是转换器用于精确捕获信号以及内置前端正确建立所需要的带宽。在多数情况下,转换器的采样带宽目标是在大约两个奈奎斯特区拨入。转换器通常也是以这种方式在其交流频率规格范围内进行表征。

设计人员在转换器指定区域外选择中频并不是个明智的选择,因为系统的交流性能结果会存在较大差异,尽管转换器数据手册中说明了额定分辨率和性能,或显示的全功率带宽远大于转换器本身的采样带宽(可能是其两倍)。设计应围绕采样带宽展开。所有设计都应当避免使用额定全功率带宽的某一或部最高频率部分,否则动态性能(SNR/SFDR)会下降。为了确定高速模数转换器的采样带宽,请查阅数据手册,或者咨询应用支持人员,因为有时候采样带宽并未明确给出。通常,数据手册会规定甚至列出转换器采样带宽内经过生产测试、能够保证额定性能的频率。然而,需要对行业中的这些带宽术语做出更好的说明和定义。

了解转换器带宽和精度

所有的ADC都存在建立时间不精确的问题。记住,转换器的内部前端必须具有足够的带宽(BW),才能精确地对信号进行采样。否则,累积误差将大于上文所述的结果。

一般而言,一个ADC的内部前端必须在半个采样时钟周期内建立(0.5/fs,其中fs =采样频率),这样才能提供对内模拟信号捕捉的精确表达。因此,对于一个12位ADC(采样速率为2.5 GSPS,满量程输入范围(VFS)为1.3 V p-p)来说,全功率带宽(FPBW)可通过下列瞬态公式推导:

求解t:

代入τ = 1/(2 × π × FPBW),一个时间常数,求解FPBW:

令t = 0.5/fs。这是样本建立所需的时间,其中采样周期为1/fs:

这样会使ADC内部前端FPBW所需的带宽最小。转换器内部前端需要这一大小的带宽,以建立至1 LSB以内并正确采样模拟信号。这将需要通过数个时间常数来满足这类ADC的1 LSB精度要求,其中1个时间常数等于24 ps或:

要了解ADC满量程范围内达到LSB大小要求所需的时间常数数量,就需要找出满量程误差%或VFSE。或1 LSB = VFS/(2N),其中N =位数;或

表1列出了不同分辨率的转换器与各自的位数、LSB大小和VFSE的关系细分表。

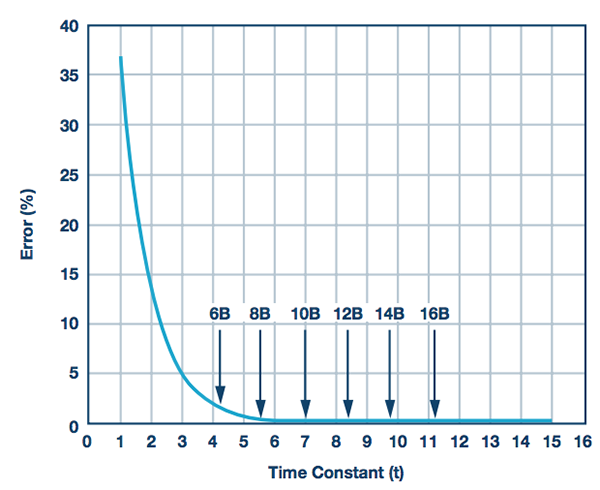

通过描绘欧拉数或eτ

,可以绘出一条曲线,以便每次通过时间常数都能方便地看出相对误差。从图2可见,12位ADC样本建立至大约1 LSB以内需时8.4个时间常数。

设计人员可通过这种分析来估算转换器能处理的最大模拟输入频率或采样带宽,并依旧建立至1 LSB误差以内。超出这个范围,则ADC无法精确表示信号。因此:

记住,这里表示的是最佳情形,并假定采用单极点ADC前端。并非所有现实中的转换器都以这种方式工作,但这是一个很好的开端。

例如,上文描述的模型最高可适用至12位。但针对14或16位以及更高位则需要采用二阶模型,因为细微的影响可使建立时间扩展至预测的一阶模型以外。

作者简介

Rob Reeder [ rob.reeder@analog.com ]是ADI公司高速转换器和射频应用集团(位于美国北卡罗来纳州格林斯博罗)的资深系统应用工程师。他发表了大量有关各种应用的转换器接口、转换器测试和模拟信号链设计的文章。Rob曾在航空航天和防务部担任应用工程师5年之久,专注于雷达、EW和仪器仪表等各种应用领域。此前,他还曾在高速转换器产品线工作9年时间。在此之前,Rob还从事过测试开发和模拟设计工作(效力于ADI多芯片产品集团),拥有5年的太空、防务和高度可靠的应用模拟信号链模块设计经验。Rob于1996年和1998年分别获得北伊利诺斯州大学(伊利诺斯迪卡尔布市)的电子工程学士(BSEE)学位和电子工程硕士(MSEE)学位。Rob晚上不写论文或在实验室研究电路时,他喜欢在健身房活动、听电子音乐、用旧木板制作家具;最重要的是和他的两个孩子一起放松自己。