作者:Walt Kester

了解基于电源抑制参数的去耦需求

在上一篇文章中,我们强调了保持低阻抗接地层对提供数字和模拟回路电流路径的重要性。本文将讨论同等重要并相关的主题:通过电源去耦来保持电源进入集成电路(IC)的各点的低阻抗。诸如放大器和转换器等模拟集成电路具有至少两个或两个以上电源引脚。对于单电源器件,其中一个引脚通常连接到地。诸如ADC和DAC等混合信号器件可以具有模拟和数字电源电压以及I/O电压。像FPGA这样的数字IC还可以具有多个电源电压,例如内核电压、存储器电压和I/O电压。

不管电源引脚的数量如何,IC数据手册都详细说明了每路电源的的允许范围,包括推荐工作范围和最大绝对值,而且为了保持正常工作和防止损坏,必须遵守这些限制。

然而,由于噪声或电源纹波导致的电源电压的微小变化—即便仍在推荐的工作范围内—也会导致器件性能下降。例如在放大器中,微小的电源变化会产生输入和输出电压的微小变化,如图1所示。

放大器对电源电压变化的灵敏度通常用电源抑制比(PSRR)来量化,其定义为电源电压变化与输出电压变化的比值。有关更详细的讨论,请参考指南MT-043。

图1显示了典型高性能放大器(OP1177)的PSR随频率以大约6dB/8倍频程(20dB/10倍频程)下降的情况。图中显示了采用正负电源两种情况下的曲线图。尽管PSRR在直流下是120dB,但较高频率下会迅速降低,此时电源线路上有越来越多的无用能量会直接耦合至输出。

如果放大器正在驱动负载,并且在电源轨上存在无用阻抗,则负载电流会调制电源轨,从而增加交流信号中的噪声和失真。尽管数据手册中可能没有给出实际的PSRR,数据转换器和其他混合信号IC的性能也会随着电源上的噪声而降低。电源噪声也会以多种方式影响数字电路,包括降低逻辑电平噪声容限,由于时钟抖动而产生时序错误。

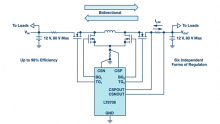

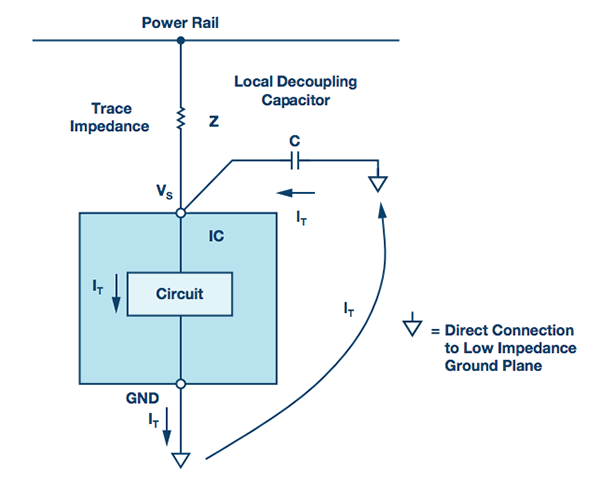

适当的局部去耦在PCB上是必不可少的

典型的4层PCB通常设计为接地层、电源层、顶部信号层和底部信号层。表面贴装IC的接地引脚通过引脚上的过孔直接连接到接地层,从而最大限度地减少接地连接中的无用阻抗。电源轨通常位于电源层,并且路由到IC的各种电源引脚。显示电源和接地连接的简单IC模型如图2所示。

IC内产生的电流表示为IT。流过走线阻抗Z的电流产生电源电压VS的变化。如上所述,根据IC的PSR,这会产生各种类型的性能降低。通过使用尽可能短的连接,将适当类型的局部去耦电容直接连接到电源引脚和接地层之间,可以最大限度地降低对功率噪声和纹波的灵敏度。去耦电容用作瞬态电流的电荷库,并将其直接分流到地,从而在IC上保持恒定的电源电压。虽然回路电流路径通过接地层,但由于接地层阻抗较低,回路电流一般不会产生明显的误差电压。

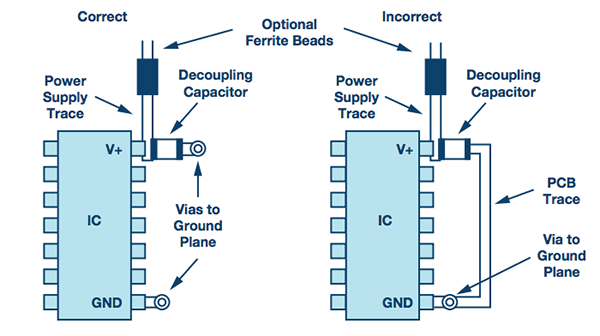

图3显示了高频去耦电容必须尽可能靠近芯片的情况。否则,连接走线的电感将对去耦的有效性产生不利影响。

图3左侧,电源引脚和接地连接都可能短,所以是最有效的配置。然而在图3右侧中,PCB走线内的额外电感和电阻将造成去耦方案的有效性降低,且增加封闭环路可能造成干扰问题。

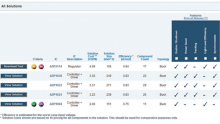

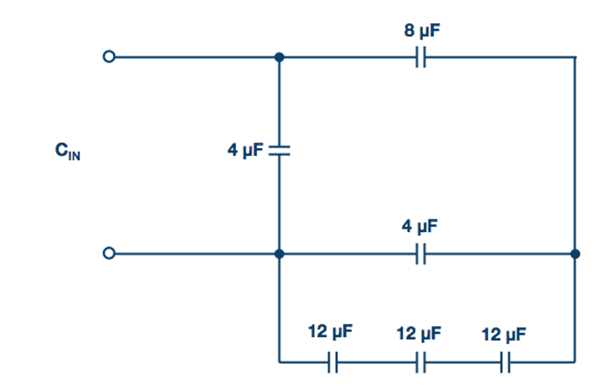

选择正确类型的去耦电容

低频噪声去耦通常需要用电解电容(典型值为1µF至100µF),以此作为低频瞬态电流的电荷库。将低电感表面贴装陶瓷电容(典型值为0.01µF至0.1µF)直接连接到IC电源引脚,可最大程度地抑制高频电源噪声。所有去耦电容必须直接连接到低电感接地层才有效。此连接需要短走线或过孔,以便将额外串联电感降至最低。大多数IC数据手册在应用部分说明了推荐的电源去耦电路,用户应始终遵循这些建议,以确保器件正常工作。

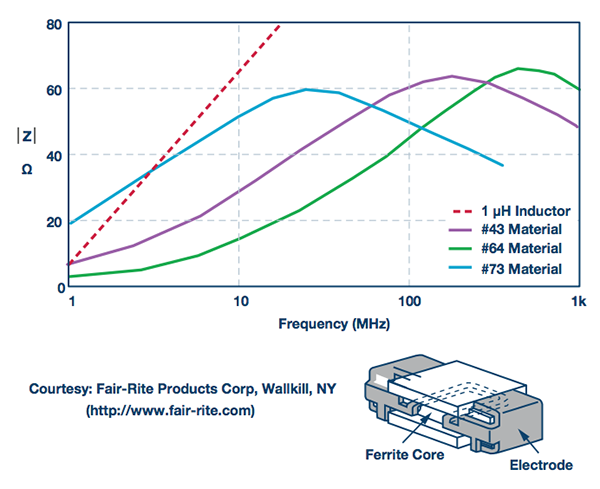

铁氧体磁珠(以镍、锌、锰的氧化物或其他化合物制造的绝缘陶瓷)也可用于在电源滤波器中去耦。铁氧体在低频下(<100kHz)为感性—因此对低通LC去耦滤波器有用。100kHz以上,铁氧体成阻性(低Q)。铁氧体阻抗与材料、工作频率范围、直流偏置电流、匝数、尺寸、形状和温度成函数关系。

铁氧体磁珠并非始终必要,但可以增强高频噪声隔离和去耦,通常较为有利。这里可能需要验证磁珠永远不会饱和,特别是在运算放大器驱动高输出电流时。当铁氧体饱和时,它就会变为非线性,失去滤波特性。

请注意,某些铁氧体甚至可能在完全饱和前就是非线性。因此,如果需要功率级,以低失真输出工作,当原型在此饱和区域附近工作时,应检查其中的铁氧体。典型铁氧体磁珠阻抗如图4所示。

在为去耦应用选择合适的类型时,需要仔细考虑由于寄生电阻和电感产生的非理想电容性能。我们将在下篇专栏中继续讨论去耦,研究各种类型的去耦电容及其应用。

所以现在我们用传统的电路测验结束本专栏。答案可在EngineerZone的StudentZone论坛®找到。

关于接地、布局和去耦的参考资料:

应用笔记AN-1142,高速ADC PCB布局布线技巧。ADI公司,2012年1月。

Ardizzoni, John。“高速印刷电路板布局实用指南”。《模拟对话》39-09,2005年9月。指南MT-100,试验板和原型制作技术。ADI公司,2009年。指南MT-101,去耦技术。ADI公司,2009年。指南MT-031,实现数据转换器的接地并解开“AGND”和“DGND”的谜团。ADI公司,2009年。

Zumbahlen, Hank。“良好接地指导原则”。《模拟对话》46-06,2012年6月。

作者介绍

Walt Kester [walt.kester@analog.com]是ADI公司企业应用工程师。在多年任职期间,他设计、开发了高速ADC、DAC、SHA、运算放大器和模拟多路复用器并提供应用支持。他撰写了许多论文和技术文章,并为ADI公司全球技术研讨会系列编撰了11本重要应用书籍;涉及的主题包括运算放大器、数据转换、电源管理、传感器信号调理、混合信号电路以及实用模拟电路设计技巧。他的最新著作数据转换手册(Newnes)近1000页,是一本关于数据转换的综合指南。Walt拥有北卡罗来纳州立大学电气工程学士学位(BSEE)和杜克大学电气工程硕士学位(MSEE)。