HMC661LC4B与HMC760LC4B THA噪声特性和分析

selina -- 周二, 05/15/2018 - 16:51

作者:Michael Hoskins

简介

采样保持 (THA) 输出噪声有两个关键噪声分量:采样噪声和输出缓冲放大器噪声。本应用笔记探讨这两个分量。

采样噪声分量

作者:Michael Hoskins

简介

采样保持 (THA) 输出噪声有两个关键噪声分量:采样噪声和输出缓冲放大器噪声。本应用笔记探讨这两个分量。

采样噪声分量

"有些信号虽然您不需要,但经常会进入系统中;这些信号称为“噪声”,我们必须了解并处理好噪声,才能成功地实现系统设计。这些噪声信号源于外部(“外部噪声”)和内部电路器件(“内部噪声”),它们具有各种特性,可以对它们进行计算并予以补偿。ADIsimPLL™是一款锁相环(PLL)电路设计和评估工具,可以协助用户评估和设计RF系统并对系统进行故障排除。该工具支持ADI公司的PLL频率合成器系列。

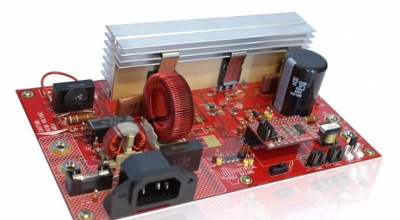

开关电源几乎用于所有电子设备中。它们由于尺寸小、成本低和效率高而具有极高的价值,但是,它们最大的缺点就是高开关瞬态导致高输出噪声。这个缺点使它们无法用于以线性稳压器供电为主的高性能模拟电路中。

简介

同步检波器可提取淹没在噪底内的小信号,用于进行各种物理量测量,例如极小的电阻、明亮背景下的光吸收或反射量,或者存在于高噪声电平下的应变。

Kazim Peker和Altug Oz ADI公司

摘要

在所有器件特性中,噪声可能是一个特别具有挑战性、难以掌握的设计课题。这些挑战常常导致一些道听途说的设计规则,并且开发中要反复试错。本文将解决相位噪声问题,目标是通过量化分析来阐明如何围绕高速数模转换器中的相位噪声贡献进行设计。本文旨在获得一种"一次成功"的设计方法,即设计不多不少,刚好满足相位噪声要求。

作者:Rob Reeder ADI公司

引言

本文介绍最常见的外部噪声源以及它们如何影响高速信号链的总动态系统性能,另外给出了一些模拟和数字小技巧,可用来改善您下一款设计的信噪比(SNR)。

简介

Kevin M. Tompsett 高级应用工程师 ADI公司

作者:Brad Brannon和Allen Barlow

孔径不确定度

作者:Brad Brannon

摘要