医疗成像系统对数据转换器的要求有多高?

selina -- 周二, 03/26/2019 - 09:10

Wilhelm Conrad Rötgen于1895年发现了X射线,让他获得了第一个诺贝尔物理学奖,也为医疗成像领域奠定了基础。

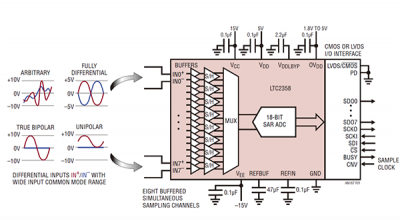

在医疗成像领域的电子设计中,数据转换器的动态范围、分辨率、精度、线性度和噪声要求带来了最严苛的挑战。本文讨论在不同成像模式环境中的这些设计挑战,并概述了能够实现最佳工作性能的高级数据转换器和集成解决方案。

数字射线照相

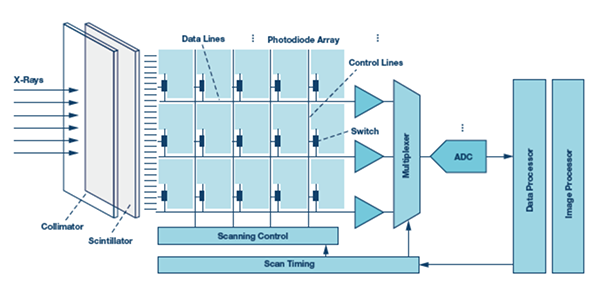

数字射线照相(DR)的物理原理与所有传统的吸收式射线照相系统相同。穿过人体的X射线经过具有不同射线穿透性的人体组织衰减并投射在平板探测器系统上,其原理如图1所示。